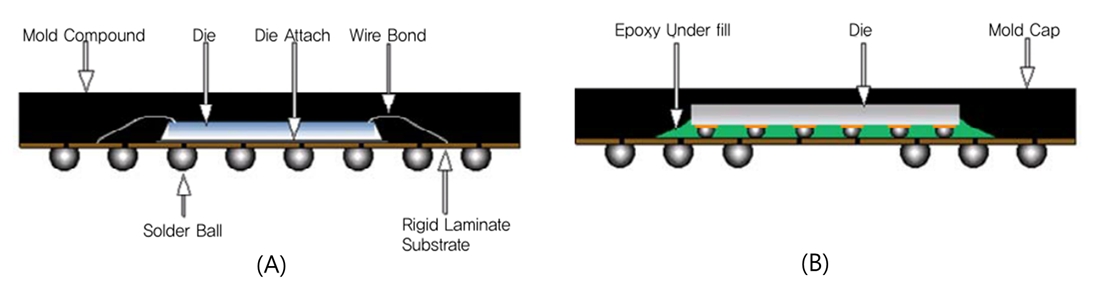

![이미지: [그림] 동사의 주요 사업 부문](%EB%8F%99%EC%82%AC%EC%9D%98%20%EC%A3%BC%EC%9A%94%20%EC%82%AC%EC%97%85%20%EB%B6%80%EB%AC%B8.jpg) |

|

[그림] 동사의 주요 사업 부문 |

주주총회소집공고

| 2025년 03 월 11 일 | ||

| 회 사 명 : | (주)다원넥스뷰 | |

| 대 표 이 사 : | 남기중 | |

| 본 점 소 재 지 : | 경기도 안산시 단원구 시화호수로 485 (성곡동) | |

| (전 화)031-8085-7899 | ||

| (홈페이지)http://www.nexview.co.kr/ | ||

| 작 성 책 임 자 : | (직 책) 경영지원실장 | (성 명) 조 현 국 |

| (전 화) 031-8085-7899 | ||

주주총회 소집공고

| (제16기 정기) |

제 16기 정기주주총회 소집통지서

주주님의 건승과 댁내의 평안을 기원합니다.

당사는 상법 제363조와 정관 제 16 조에 의거 제 16기 정기주주총회를 아래와 같이 개최 하오니 참석하여 주시기 바랍니다.

- 아 래 -

1. 일 시 : 2025년 03월 27일(목요일) 오전 09시 00분

2. 장 소 : 경기도 안산시 단원구 시화호수로 485 ㈜다원넥스뷰 1층 회의실

3. 회의 목적 사항

가. 보고사항 : ①감사보고 ②영업보고 ③내부회계관리제도 운영실태보고

나. 부의안건

제1호 의안 : 제 16기 (2024.01.01~2024.12.31) 재무제표 승인의 건

제2호 의안 : 정관 일부 변경의 건

제3호 의안 : 이사 선임의 건

제3-1호 의안 : 비상무이사 박병철 신규 선임의 건

제4호 의안 : 감사 선임의 건

제4-1호 의안 : 감사 한일영 신규 선임의 건

제5호 의안 : 이사 보수한도액 승인의 건(1,500백만원)

제6호 의안 : 감사 보수한도액 승인의 건(60백만원)

4. 배당내역 : 해당없음

5. 경영참고사항 비치

상법 제542조의4에 의한 경영참고사항은 당사 인터넷 홈페이지에 게재하고 본점과 명의개서대행회사(국민은행 증권대행부)에 비치하였으며, 금융위원회 및 한국거래소에 전자공시하여 조회가 가능하오니 참고하시기 바랍니다.

2025년 03월 11일

주식회사 다원넥스뷰

대표이사 남 기 중 (직인생략)

I. 사외이사 등의 활동내역과 보수에 관한 사항

1. 사외이사 등의 활동내역

가. 이사회 출석률 및 이사회 의안에 대한 찬반여부

| 회차 | 개최일자 | 의 안 내 용 | 이사 등의 성명 | ||

|---|---|---|---|---|---|

| 유영진 | 김후식 | 박하진 | |||

| (출석률:100%) | (출석률:100%) | (출석률:100%) | |||

| 찬반 여부 | |||||

| 1 | 2024.02.14 | 주요사항보고서(합병변경 계약의 건 ) | 찬성 | - | - |

| 2 | 2024.02.23 | 내부회계 운영실태,결산 재무제표 이해관계자 거래 총액 승인 | 찬성 | - | - |

| 3 | 2024.03.07 | 주주총회 소집결의 | 찬성 | - | - |

| 4 | 2024.03.14 | 합병계약 체결, 임시주주총회 소집결의 | 찬성 | - | - |

| 5 | 2024.03.26 | 대표이사 중임, 사외이사 겸업, 이사 보수 결정의 건 | 찬성 | - | - |

| 6 | 2024.03.26 | 합병 변경계약 체결의 건 (수정) | 찬성 | - | - |

| 7 | 2024.04.29 | 은행 신규 대출의 건 | 찬성 | 찬성 | 찬성 |

| 8 | 2024.05.27 | 합병경과 보고의 건 | 찬성 | 찬성 | 찬성 |

| 9 | 2024.05.27 | 우리사주 무상 출연의 건 | 찬성 | 찬성 | 찬성 |

| 10 | 2024.06.03 | 코넥스시장 상장 폐지 및 코스닥시장 상장 결의의 건 | 찬성 | 찬성 | 찬성 |

| 11 | 2024.11.21 | 기업은행 대출 연장의 건 | 찬성 | 찬성 | 찬성 |

주) 2024.03.26 사외이사 박하진, 김후식 선임

나. 이사회내 위원회에서의 사외이사 등의 활동내역

- 해당사항 없습니다.

2. 사외이사 등의 보수현황

(단위 : 백만원)

| 구 분 | 인원수 | 주총승인금액 | 지급총액 | 1인당 평균 지급액 |

비 고 |

| 사외이사 | 3 | 1,000 | 12 | 4 | - |

※ 주총승인금액은 사내이사 2명을 포함한 등기이사 전원의 보수한도 총액입니다.

II. 최대주주등과의 거래내역에 관한 사항

1. 단일 거래규모가 일정규모이상인 거래

| (단위 : 억원) |

| 거래종류 | 거래상대방 (회사와의 관계) |

거래기간 | 거래금액 | 비율(%) |

|---|---|---|---|---|

| - | - | - | - | - |

2. 해당 사업연도중에 특정인과 해당 거래를 포함한 거래총액이 일정규모이상인 거래

| (단위 : 억원) |

| 거래상대방 (회사와의 관계) |

거래종류 | 거래기간 | 거래금액 | 비율(%) |

|---|---|---|---|---|

| - | - | - | - | - |

III. 경영참고사항

1. 사업의 개요

가. 업계의 현황

당사는 반도체 테스트 및 반도체 패키징 공정에 필요한 공정 장비 및 기기 등을 주력 제품으로 사업을 확대 성장시켜 나가고 있는 기업으로 반도체 제조업을 가장 중요한 전방산업으로 두고 있습니다. 동 전방산업은 대표적인 자본 집약형 장치 산업으로 최종 매출처의 설비투자 계획에 따라 후방 산업의 업황이 영향을 받는 구조입니다. 동사가 속한 반도체 장비 시장은 반도체 산업의 경기사이클에 지속적인 영향을 받습니다.

당사의 반도체 테스트 부문의 주력 시장인 메모리용 웨이퍼 프로브카드 시장은 내수의 경우 국내 신규 투자를 주도하던 Nand Flash용 프로브카드 시장이 COVID-19 특수로 인해 발생한 슈퍼 사이클이 종식되고 신규 투자가 Slow한 상태로 접어든 반면, 해외 시장의 경우 중국의 반도체 굴기, 전 세계적인 경제 안보화로 가속화된 반도체의 자국 생산화 연속성 상에서 중국 시장이 자국의 Nand Flash 양산을 전후하여 프로브카드 제조에도 공격적인 신규 선투자를 이어가고 있습니다.

현재 메모리용 프로브카드 시장에 가장 큰 전환점은 미국과 일본의 제조사가 독점하고 있는 DRAM용 프로브카드 시장이 국내 제조사의 내재화 성과에 힘입어 초도 양산을 위한 선투자가 진행되어 본격적인 양산 진입 시 전체 프로브카드 시장의 판도 변화가 예상되며, 특히 최첨단 AI, 자율주행, 데이터센터 등 고성능 반도체 프로세서 수요로 촉발된 HBM (High Bandwidth Memory)시장의 성장이 동반되어 기존 DDR기반 메모리 대비 테스트 종류가 늘어나면서 동사가 속해 있는 후방산업이 직접적인 수혜를 받을 것으로 기대하고 있습니다.

당사의 반도체 패키징 부문의 주력 시장인 FC-BGA 기판 시장 역시 HBM의 최대 수요처인 고부가 2.5D 반도체 패키징 시장의 필수 부품으로 동일한 성장 요인의 적용을 받고 있으며, 이로 인해 필연적인 반도체 기판의 다층화 및 대면적화는 제조 공정에서는 수율 확보가 진입 장벽이 되었고, 제품의 고가화는 불량에 따른 품질 비용의 기하급수적인 증가가 현실화되면서 동사가 대기업에 반복 납품하면서 신규로 사업화에 성공한 최종 단계의 마이크로 범프 리페어 시장의 급속한 성장을 견인해 나갈 것으로 예상됩니다.

이와 같이 동사 제품의 주력 시장은 반도체 테스트 부문에서 HBM으로 대표되는 3D패키징 시장과 성장 궤도를 같이 하고, 반도체 패키징 부문에서는 FC-BGA로 대표되는 차세대 2.5D 패키징 시장에 직접적인 영향을 받고 있어, 이러한 전방산업이 제공하는 최첨단 기술 트렌드에 기반한 성장요인은 중장기적으로 동사 사업의 견고한 성장 토대가 될 것으로 예상됩니다.

나. 회사의 현황

(1) 영업개황 및 사업부문의 구분

(가) 영업개황

당사는 핵심기술인 'LSMB (Laser Systemic Micro-Bonding)' 라는 차별화된 기술로 첨단 산업에 필요한 초정밀 공정 장비를 개발 및 제조하여 제품화하였으며, 현재 반도체 테스트 공정과 반도체 기판 제조 및 패키징 공정에 필요한 레이저 마이크로 접합 공정 제품을 중심으로 전/후 공정까지 자동화할 수 있는 Tunkey 제품까지 라인업하여 사업을 확대해 나가고 있습니다.

당사의 사업화가 완성된 주요 제품은 반도체 웨이퍼를 테스트하기 위한 프로브카드에 탐침(Probe)를 초정밀 접합하는 'pLSMB(Probe Laser Systemic Micro-Bonding)제품군'과 반도체 패키징 또는 기판의 Micro Solder Ball을 Bumping하는 'sLSMB(Solder Laser Systemic Micro-Bonding)제품군'이 있으며, 신규 사업 확대를 위해 디스플레이, 솔라셀, 스마트폰에 소요되는 부품소자를 정밀 가공하거나 접합하는 공정 장비를 제품화해 나가고 있습니다. 사업화가 완성된 주력 제품의 세부 제품 목록은 아래와 같습니다.

|

분류 |

제품군 |

주요 사용 범위 |

|

반도체 테스트 |

pLSMB |

DRAM 또는 Nand Flash 메모리 웨이퍼에서 CIS (CMOS Image Sensor), DDI (Display Driver IC) 비메모리 웨이퍼에 이르기까지 완성된 웨이퍼를 Die 단위로 절단하여 패키징하기 전에 웨이퍼 상태에서 검사하기 위한 프로브 카드를 제조하는 공정에 사용됨. 30-40㎛ 두께의 탐침을 레이저로 마이크로 접합하는 Laser Micro-Bonding System 핵심 장비를 중심으로 전단계에서 MEMS 방식으로 웨이퍼 상태로 제작된 프로브(탐침)의 연결부를 레이저로 절단하여 분리시켜 주는 Probe Cutting 장비, Probe의 연결부가 절단된 웨이퍼 상태에서 접합 공정을 위한 Tray에 삽입하는 Probe Inserting 장비 그리고 완성된 프로브 카드 탐침의 접촉부를 비전으로 검사하는 Wafer Inspection 장비와 완성된 프로브카드 상에서 불량 탐침을 제거하고 리본딩하는 Laser Micro-Repair 장비를 Line-Up으로하여 Turnkey 공급하고 있음. |

|

반도체패키징 |

sLSMB |

반도체 패키징 공정의 칩과 반도체 기판의 입출력 단자를 연결하는 방식이 기존의 Wire Bonding 방식에서 Solder Bump를 이용한 Flip Chip 접합 방식으로 바뀌어 감에 따라 반도체 패키징 또는 기판 제조 공정 중 Solder Ball을 Bumping하는 제조 공정에 사용됨. 당사는 레이저 솔더볼 젯팅 프로세스를 통해 플립칩 기판의 칩 연결 단자로 사용되는 직경 40~80㎛ 크기의 플립칩 스케일 Micro-Bump를 접합을 위한 제품을 Flagship으로 하여, 반도체 기판과 최종 제품 PCB 기판의 입출력 단자를 접합하는 데 활용되는 직경 150~760㎛ 크기의 BGA 스케일 Bump를 접합하는 장비로 이원화하여 웨이퍼 레벨 패키지, BGA 패키지 제조 공정과 동일한 솔더볼 스케일로 입출력 단자를 솔더링하는 스마트폰 카메라 모듈, Wearable 센서류 등의 제조 공정에 단독 공정 장비 또는 자동 물류 라인을 구성하여 공급하고 있음. |

[표] 주요 제품의 사용 범위

![이미지: [그림] 동사의 주요 사업 부문](%EB%8F%99%EC%82%AC%EC%9D%98%20%EC%A3%BC%EC%9A%94%20%EC%82%AC%EC%97%85%20%EB%B6%80%EB%AC%B8.jpg) |

|

[그림] 동사의 주요 사업 부문 |

(나) 공시대상 사업부문의 구분

당사의 사업부문별 내용은 다음과 같습니다.

(1) 반도체 테스트 부문 (pLSMB 사업 부문)

반도체 제조공정 중 반도체 소자의 전기적 기능 테스트 공정에 프로브카드(Probe Card)가 소요되며, 당사는 프로브카드 제작에 필요한 공정 자동화 장비를 개발, 제조 및 판매하고 있습니다. 반도체 제조공정은 크게 웨이퍼를 제조하는 전공정과 제조된 웨이퍼를 가공하여 각각의 반도체 칩을 생산하는 후공정으로 구분됩니다. 전공정은 웨이퍼상에 설계된 회로에 따라 여러 종류의 막을 형성하고 불필요한 부분을 제거하는 과정을 반복하며 전자회로를 형성하는 공정입니다. 후공정은 개별 칩별로 전기적 신호를 연결하고 형상 가공의 역할을 하는 패키징 공정과 반도체 소자의 전기적 기능을 검사하는 테스트 공정으로 분류됩니다.

당사의 제품이 사용되는 테스트 공정은 다시 패키징 이전 단계인 웨이퍼 상태에서 진행되는 웨이퍼 테스트(Wafer Test)와 패키징 공정 완료 후 완성된 개별 칩에 대한 검사를 수행하는 패키지(PKG Test) 테스트로 구분됩니다. 당사의 주요 제품인 프로브카드는 웨이퍼 테스트(Wafer Test)에 소요되는 고부가가치의 소모성 부품입니다. 프로브 카드는 웨이퍼 상태에서 웨이퍼 내에 제작된 칩의 전기적 동작 상태를 검사하기 위해 Probe(탐침)을 일정한 규격의 회로기판에 부착한 카드로, Probe의 Contact부가 웨이퍼에 생성된 칩 내부의 패드(Pad)에 접촉되면서 메인 테스트 장비로부터 받은 신호를 전달하고 칩에서 출력되는 신호를 감지하여 다시 메인 테스트 장비에 전달하는 역할을 수행합니다. 테스트 장비는 전달된 신호를 받아 칩의 양, 불량을 확정하게 되므로 프로브 카드는 웨이퍼와 테스트 장비의 중간 매개체입니다.

제품 수율 향상을 위하여 웨이퍼 제작 후 패키징을 하기 전 검사를 통해 불량 칩을 판별하여 주는 것을 EDS (Electrical Die - Sorting Test) 검사라고 합니다. EDS 검사는 반도체 검사 장비에서 발생되는 신호를, 웨이퍼 패드와(Wafer Pad)와 프로브카드를 Probing 해주는 Probe station을 통해 인가하여 주는 방식으로 이루어집니다. 웨이퍼 패드를 프로브 팁(tip)이 접촉한 상태에서 신호를 입력하고 출력되는 신호를 감지하여 전기적 검사를 하는 장비를 ATE (Automatic Test Equipment)라고 하며. 프로브카드는 ATE와 웨이퍼 사이의 전기적 신호를 전달해주는 핵심역할을 하는 부품입니다. 프로브카드는 동시에 다수의 칩을 최소한의 시간에 정확하게 테스트를 수행할 수 있는지 여부가 핵심 기술로, 테스트 효율을 제고시키기 위해 절대적으로 필요한 부품 소재인 반면, 반도체 제조사의 생산기술에 동조화되어야 하므로 기술적 진입장벽이 높은 분야입니다. 또한 제품의 신뢰성 확보가 매우 중요한 경쟁력이므로 장기간의 개발 및 양산 경력과 고객사와의 신뢰관계가 요구됩니다.

|

2000년 이전에는 주로 핀을 기판에 수작업으로 본딩하는 형태로 제조된 프로브카드를 이용하여 웨이퍼 테스트 공정에 적용하였습니다. 그러나 웨이퍼의 크기는 확대되는 반면 칩은 소형화 되면서 검사 칩수가 제한적인 수작업 조립형태의 제품은 한계에 봉착하였습니다. 특히, 최근 반도체 소자는 고집적화로 회로 선폭 및 칩 내부에 생성되는 입출력 패드 사이의 간격이 미세해 지면서 프로브카드에도 높은 정밀도 및 미세화에 대한 대응이 요구되나 기존 수작업 형태의 제품은 대응이 불가하게 되었습니다. 이에 프로브카드 제조사들은 수작업이 아닌 반도체 식각 방법을 이용하여 초소형 정밀 기계 기술로 각광받는 멤스(MEMS, Micro Electronic Mechanical System) 기술을 기반으로 한 멤스 프로브카드를 개발하였습니다. 멤스 프로브카드는Probe 의 제작 공정으로 반도체 식각 방법을 이용한MEMS(Micro Electro Mechanical System) 공정으로 형성되며, Probe의 초소형화 및 협 피치에 대응할 수 있다는 관점에서Advanced Probe Card라고도 합니다. MEMS는 반도체 공정기술을 기반으로 한 초소형 정밀기계 제작기술로, 초소형 제품의 대량 생산이 가능하여 프로브카드를 비롯하여 자이로 센서, 가속도 센서, 프린터 헤드, 미세 기계 분야 등에 광범위하게 적용되고 있습니다.

|

MEMS 기술을 활용한 프로브카드는 테스트 시간과 비용을 줄일 수 있고, 프로빙(Probing)의 정확도 및 반복 테스트 등에서 탁월한 성능을 발휘하여 초기에는 DRAM 제품의 웨이퍼 테스트용으로 적용되었으나, 이후 Nand Flash용 제품은 물론 비메모리용 제품까지 반도체 산업 내에서 적용분야가 확대되고 있습니다. CIS (Camera Image Sensor)와 같은 비메모리용 MEMS 프로브카드를 비롯하여 최종 패키지 테스트에 사용되는 테스트 소켓 및 디스플레이를 구동하는 Driver IC 테스트 카드까지 MEMS 프로브 제품의 포트폴리오가 지속적으로 확대되고 있습니다.

|

당사는 2D MEMS 프로브카드 제작 장비 중 프로브 기판(세라믹) 위에 형성된 패턴 전극(PAD)에 프로브(탐침)을 하나씩 정밀 본딩(bonding)하는 장비인 ‘Laser Micro-Bonding System’을 개발하였습니다. 동 장비는 전 세계 상용화된 레이저 마이크로 접합 장비 중에서 가장 높은 정밀도가 요구되는 제품 중 하나입니다. 당사는 메모리용 웨이퍼를 테스트하는 데 필요한 60um이하 간격으로 프로브카드 위에 MEMS 타입의 프로브 핀을 2만개(낸드 플래시용)에서 10만개 (DRAM용)까지 본딩하고, 본딩 후 전체 핀의 정밀도를 4 ~ 5um 오차 이하 요구 수준을 만족시켜 양산 적용에 성공하였습니다.

|

또한 이 장비에 필요한 레이저 응용 기술은 물론 ±1um Stage 정밀도를 구현하기 위한 세계 최고 수준의 기구 설계 및 조립 기술, 2D스테이지 맵핑(Stage Mapping) 기술, 3차원 고속 오토 포커스 비전(3D Auto Focus Vision) 기술 등은 기술 차별화를 통한 사업 영역 확대에 근간이 되고 있습니다. 전 세계 메모리 생산의 70% 이상인 안정적인 국내 시장을 기반으로 세계 1위 미국 프로브카드 업체부터 신규 중국 및 대만 신규 업체에 이르기까지 납품하고 있으며, 또한 전체 MEMS프로브카드 시장의 절반 이상으로 성장한 비메모리용 프로브카드 시장에서도 CIS (CMOS Image Sensor)와 DDI (Display Driver IC)용 프로브카드를 중심으로 응용 분야를 확대해 나가고 있습니다.

|

한편, MEMS 방식의 프로브카드 종류에는 제작 방식에 따라 크게 3D MEMS 방식과 2D MEMS로 구분할 수 있습니다. 3D MEMS는 반도체 식각 방법을 이용하여 프로브 핀을 직접 생성시키며, 2D MEMS의 경우 프로브(탐침)을 반도체 식각 공정으로 별도 제조하고 Probe를 기판에 레이저 마이크로 본딩 기술을 이용하여 접합하는 방식으로 제조합니다.

초기 DRAM용 프로브카드에 요구된 Fine Pitch 대응 문제와 대면적 제작에 대한 효율성 문제를 해결하기 위하여 미국의 Formfactor사가 시초가 되어 3D MEMS방식이 시장을 주도하였으나, 일본의 MJC사가 2D MEMS 방식으로 DRAM용 프로브카드 제작에 성공한 것을 계기로 New 2D MEMS Probe Card 시장이 열렸습니다. 3D MEMS의 경우 일괄 공정인 장점은 있지만 적층해야 되는 높이가 Probe의 세워진 높이만큼이라 적층 공정의 반복 회수가 많아 수율이 낮고 필수적인 12인치 웨이퍼 Fab.구축으로 투자비가 많이 들어가는 반면, 2D MEMS의 경우 기판과 핀의 제조공정이 분리되어 있어 6~8인치 웨이퍼 Fab.의 구축만으로 양산이 가능하여 상대적으로 초기 투자비가 적으며, 적층해 나가는 높이가 Probe의 두께에 해당되어 적층 반복 회수가 작아 심플한 공정으로 수율이 높습니다. 주요 프로브카드 제조사들의 매출을 기준으로 추정 시, MEMS 프로브카드 시장의 1, 2위 수요처인 삼성전자와 SK하이닉스에서 3D와 2D의 비중은 과거 3 : 7 수준인 것으로 파악되었으나 현재 Nand Flash용 프로브카드의 경우 사실상 2D MEMS방식으로 일원화되었고, 신규 투자는 2D MEMS에 국한되어 증설되고 있어 향후 2D MEMS의 비중이 더욱 높아질 것으로 예상됩니다. 3D MEMS방식과 2D MEMS방식의 상호 제조 공정상의 차이점을 요약하면 아래와 같습니다.

|

|

3D MEMS 프로브카드 |

2D MEMS 프로브카드 |

|

|---|---|---|

|

장점 |

-. 정밀도 구현이 용이함 -. Fine Pitch대응이 유리함 -. 일괄 공정에 의해 제작됨. (Lithography, Etching, Electroplating, Deposition) |

-. 프로브 및 본딩 기술의 진화로 Fine Pitch 대응 가능 -. Probe 두께만큼 반복되는 단순한 MEMS공정으로 제조 수율이 높음 -. 동일한 형상의 프로브로 구성되어, 유지보수가 쉬움 -. 공간 변화기(STF: Space Transformer)의 MLC 제작 용이 |

|

단점 |

-. 12인치 웨이퍼 Fab 공정으로 투자비 부담이 큼 -. Probe 높이만큼 연속되는 반복 MEMS공정으로 수율이 낮음 -. 다양한 Probe 형상으로 구성되어 유지보수가 어려움 -. 공간 변화기(STF: Space Transformer)의 MLC 제작 난해 |

-. Probe제작과 Probe Card제조 공정이 분리된 공정으로 제작됨. -. 정밀도 구현이 상대적으로 난해하고 본딩 장비 의존도 높음 |

[표] 3D MEMS와 2D MEMS 방식의 비교

(2) 반도체 패키징 부문 (sLSMB 사업 부문)

당사의 sLSMB(Solder Laser Systemic Micro-Bonding)사업부문은 Laser Micro-Solder Ball Jetting 프로세스를 바탕으로 전방산업인 반도체 산업 중 반도체 후공정인 패키징 공정용 장비 시장을 목표 시장으로 하여 사업을 확대해 가고 있습니다. 반도체는 1947년 미국의 벨연구소에서 세계최초로 트랜지스트 개발에 성공하고, 1958년 미국의 텍사스인스트루먼트 (TI: Texas Instrument)라는 회사에서 다수의 트랜지스터가 하나의 공간에서 집적되는 집적회로 (IC: Integrated Circuit)를 개발한 이래 반도체 산업은 주로 집적도 향상 및 통합에 주력해왔으며, 1965년 인텔의 공동 설립자인 고든 무어가 ‘반도체의 집적도는 18개월마다 2배씩 증가한다’는 “Moore’s Law”는 반도체 개발자와 생산자들에게 시장 생존의 법칙으로 자리 잡아 왔습니다.

반도체 기술 중 웨이퍼에 반도체 회로를 구현하는 전 공정의 발전이 현재는 소자간 간격 축소 및 종횡비 상승으로 전 공정 기술을 통한 성능 및 집적도 개선 한계에 봉착, 이러한 환경 속에 28nm 이하의 반도체 전 공정 투자에 대한 비용이 증가하고 있기 때문에 반도체 전 공정 기술의 한계를 극복하고, 저전력, 고성능, 소형 반도체를 위해 미세공정의 대안으로 반도체 패키징 기술이 주목받고 있는 상황입니다.

![이미지: [그림] 반도체 제조공정의 기술적 한계 (출처:SEMATECH)](1.jpg) |

|

[그림] 반도체 제조공정의 기술적 한계 (출처:SEMATECH) |

일반적으로 반도체 칩은 수많은 미세 전기 회로가 집적되어 있으나 그 자체로는 반도체 완성품으로서의 역할을 할 수 없으며, 외부의 물리적 또는 화학적 충격에 의해 손상될 가능성이 존재합니다. 따라서 반도체를 패키징하는 가장 큰 목적은 (1) 반도체 칩에 필요한 전원 공급, (2) 반도체 칩과 메인 PCB간의 신호 연결, (3) 반도체 칩에서 발생되는 열 방출, (5) 반도체 칩을 외부의 습기나 불 보호하기 위함이었습니다.

![이미지: [표] 반도체 패키징의 목적](2.jpg) |

|

[표] 반도체 패키징의 목적 |

반도체 패키징 기술은 크게 BGA (Ball Grid Array)와 FC (Flip Chip)이라는 두 단계의 큰 변화가 전체 시장의 판도를 바꾸는데, 첫 번째 진화인 BGA는 1세대 리드프레임 (Lead Frame) 계열의 패키지들이 구리 동판에 에칭을 해서 배선을 만드는 방식에서 리드프레임 대신에 기판을 PCB로 대체한 것으로, PCB는 여러 층으로 배선층을 구성할 수 있고, 각각의 배선층을 Via를 통해 수직으로 연결할 수 있어 패키지 아래 전체 면적에 입출력 단자를 구성할 수 있는 장점을 이용하여, I/O 단자 수가 획기적으로 증가시킨 것입니다.

|

|

Wire Bonding Interconnection (A) 와 Flip Chip Bonding Interconnection (B) |

두 번째 큰 진화인 반도체 칩과 기판의 연결 방식 또한 기존의 금속선을 이용한 Wire Bonding 방식 대신에 반도체 칩의 외부 입출력 단자인 패드 위에 미세한 돌기, 즉 범프(Bump)를 형성시켜 뒤집어 연결하는 Flip Chip Bonding 방식으로 높은 핀 카운트 및 빠른 데이터 처리 속도를 구현하는데 현재 Flip Chip 패키지는 Advanced Package의 80% 점유율을 차지할 만큼 근간이 되었습니다.

4.jpg[그림] 첨단 반도체 패키지별 매출 점유율 (출처:Yole Developpement)

이러한 BGA 계열의 기판과 FC 계열의 반도체 칩에 기반한 패키징 기술은 ‘솔더볼’이라는 새로운 소재의 도입과 급속한 시장 확대를 불러 왔습니다. 고집적 반도체 칩의 실장에 적용되는 BGA 패키지는 일정한 간격(Grid)으로 배열된 솔더볼을 용융시켜 칩과 제품 기판를 연결하는 방식을 말하는데, 이를 위해서는 솔더볼이 필수적으로 요구되며, 현재 다양한 제품군에 활용되고 있습니다. 또한 첨단 반도체 칩의 회로가 더욱 미세화되고, 패키징 공정기술이 발전함에 따라 FC 계열의 마이크로 솔더볼(Microscale Solder Ball)의 수요가 확대되고 있습니다.

![이미지: [그림] BGA 적용 분야 (출처: 한국전자통신연구원)](5.jpg) |

|

[그림] BGA 적용 분야 (출처: 한국전자통신연구원) |

기술한 바와 같이 반도체 패키징(Packaging)의 발전 과정은 다기능화에 따른 경박단소화가 핵심적인 Drive로 작용하여 반도체 칩의 3D 적층까지 실현되었습니다. 그럼에도 불구하고, 여전히 다기능화와 더 많은 입출력 단자 수에 대한 요구는 계속되고 있어, 궁극적으로는 반도체 칩 간의 연결 방식 뿐만 아니라 Wafer Level에서나 Substrate Level에서 메인 PCB 패드와의 연결 입출력 단자 수도 우선적인 증가 요구에 직면하고 있습니다. 동일한 공간 내에서 더 많은 입출력 단자를 만들기 위해서 가장 선호되는 방법은 단자 간의 피치를 최소화하는 것이며, 결국 이를 위해서는 Bump의 크기가 축소되어야 실현이 가능합니다. 고성능 CPU, GPU, 스위치 기판으로 활용되는 FC-BGA, FC-CSP와 같은 FC 기판 등은 향후 30um 이하 크기의 Micro Solder Ball을 적용한 기판까지 개발 중에 있습니다.

FC-BGA는 전통적으로 CPU, GPU, FPGA(Field Programmable Gate Array), ASIC 등 고성능 프로세서를 위해 사용됩니다. 이들 프로세서는 주로 DRAM, 칩셋 등과 함께 패키지화되고, 최근에는 모듈형 디자인 형태의 칩렛(Chiplet)의 활용이 늘어나는 추세입니다. 이 때문에 FC-BGA도 멀티칩 모듈화(MCM)되고 있고, Die간 고속 상호연결 기술에 대한 요구가 늘어나고 있어 FC-BGA의 패키지 크기는 20~80㎜가 되었고, 기판 층수는 6층에서 22층까지 확대되었습니다. 또한 더 촘촘한 간격의 Flip chip Bump를 구현하는 방향으로 진화하고 있어 대체로 10층 미만이지만, 최근 24층(11-2-11) 구조까지 고도화되었습니다. 대면적 FC-BGA는 고성능 컴퓨팅, 데이터 서버, 통신에 사용되는 고성능 CPU, GPU, 스위치 등에 채용되는데, 클라우드 컴퓨팅, 인공지능, 고속 통신 트렌드를 위해 필수적입니다. 이러한 고성능 프로세서는 200㎟ 이상의 대면적 Die와 1,000~10,000개에 이르는 많은 I/O를 가지며, 최적의 성능을 위해 메모리나 다른 프로세서와 함께 비싼 패키지 기판을 사용합니다.

![이미지: [표] FC-BGA 기술 트렌드(출처: Prismark, 키움증권)](6.jpg) |

|

[표] FC-BGA 기술 트렌드(출처: Prismark, 키움증권) |

대면적 FC-BGA의 대표적 사례인 AMD의 Zen 2 서버 프로세서와 Intel의 Xeon 서버 CPU의 경우 두 제품의 기판 크기는 각각 75.4 x 58.5㎜, 76.0 x 56.5㎜에 달하고, AMD의 Zen 2 서버 프로세서는 여러 개의 대형 Die를 통합했고, 20층(9-2-9) 구조에 회로 선폭은 12㎛를 구현했습니다. 이 외에도 Intel Xeon Platinum 9200 CPU용 FC-BGA 크기는 72.5 x 76.0㎜, HiSilicon HI1620 서버 프로세서용 FC-BGA 크기는60 x 75㎜로 대면적 FC-BGA는 고성능 제품을 중심으로 빠르게 적용되고 있습니다.

![이미지: [그림] 대면적 FC-BGA 사례 (출처:AMD, Primask, AnandTech, HiSilicon)](7.jpg) |

|

[그림] 대면적 FC-BGA 사례 (출처:AMD, Primask, AnandTech, HiSilicon) |

이러한 Micro Solder Ball이 적용되는 대면적 FC-BGA 기판의 도입은 단순하게 Solder Ball과 Pad의 Size의 축소에 국한되지 않으며, 새로운 공정 기술과 새로운 생산 설비의 수요를 일으키고 있습니다. 실제 Solder Ball Size가 축소될수록 Reflow 공정과 Deflux 공정 이후에 Solder Ball이 탈락되는 ‘Missing Bump’와 같은 불량의 비중이 심각할 정도로 증가하며, 이러한 제품은 FC-BGA 크기가 2배, 3배로 커지면 4배, 9배로 면적은 커지는데 대면적 때문에 수십만개의 솔더볼 중 하나만 탈락해도, 10% 이상의 수율 감소로 직결되어 Repair 공정 없이는 시장에서 요구되는 수율과 Cost를 만족시킬 수가 없습니다.

![이미지: [그림] 대면적 FC-BGA 솔더볼 누락 불량의 리페어 전후](8.jpg) |

|

[그림] 대면적 FC-BGA 솔더볼 누락 불량의 리페어 전후 |

기존의 솔더볼 범핑 표준 공정은 기판에 플럭스를 사전 도포하고, 그 위에 솔더볼을 실장하여 광학식 비전 검사를 하고 솔더볼이 누락된 패드 위에 다시 솔더볼을 실장하고 리플로우 솔더링 및 플럭스 세정을 하는 공정이었습니다. 이 경우에는 리플로우 솔더링 이전에 진행되는 공정이기 때문에 단순하게 솔더볼만 다시 누락된 위치에 실장하면 되는 간단한 공정입니다. 물론 리플로우 솔더링과 플럭스 세정 중에 솔더볼이 누락되는 불량이 발생하나, 양산에 적용 가능한 리페어 방법이 부재하여 이후 발생하는 불량에 대해서는 전량 폐기해 오고 있었습니다. 하지만, 기판이 고층화되어 상당한 원가 상승이 발생하고, 대면적화되면서 생산능력 잠식효과가 커져, 최종 단계에서의 리페어 솔루션이 기판 업체에서는 가장 시급한 현안이 되었습니다.

이러한 현안에 대한 솔루션을 제공하기 위해 솔더볼 실장과 동시에 용융 접합이 가능한 Substrate LSMB 기술인 ‘Laser Solder Ball Jetting’ 프로세스를 기반으로 일괄 리페어 공정 자동화 장비를 개발, 세계 굴지의 글로벌 CPU 기업에 기판을 제조하는 국내 대기업에 판매하여 세계 최초로 양산 적용에 성공하였습니다.

![이미지: [그림] Laser Solder Ball Jetting Process](111.jpg) |

|

[그림] Laser Solder Ball Jetting Process |

![이미지: [그림] Laser Solder Ball Jetting](10.jpg) |

|

[그림] Laser Solder Ball Jetting |

현재 당사가 1차적으로 목표하고 있는 제품의 시장은 고성능 패키지 기판을 대표하는 Flip Chip 기판 제조 공정입니다. Flip chip 기판의 침투율은 IC의 24%이자 MPU/GPU/AP의 100%이고, 전체 웨이퍼 면적의 21%, 패키징 매출의 33%, Die 레벨 상호연결(Interconnect)의 70%를 차지하고 있습니다. 성능 뿐만 아니라 원가 효율성과 더 작은 Form Factor의 강점으로 작은 형상과 낮은 전압으로 인해 Die 코어까지 전력 분배 효율성을 향상시키고, 변환 속도를 높일 수 있으며, 패키지의 열적 성능을 향상시키고, CSP 만큼 작은 패키지 사이즈를 구현하며, 1,000개 이상의 I/O를 가진 고성능 패키지의 원가를 낮출 수 있는 장점이 있습니다. 또한 세부 목표 시장인 FC-BGA, FC-CSP, 고밀도 Fan-Out, 2.5D/3D 솔루션을 포함한 고성능 패키지 기판은 전체 패키지 시장에서 수량 기준 3% 미만이지만, 금액으로는 25%를 차지하고 있으며, MCM, 2.5D, FO-MCM, 3D TSV(Through Silicon Via) 등 이른바 Multi-Die 패키징 솔루션의 확산에 따라 Flip chip 기판의 웨이퍼 면적과 매출액 기준 성장률은 훨씬 높아지고 있습니다.

![이미지: [그림] Advanced IC Substrate 시장 성장율 (출처: Yole Intelligence 2023)](11.jpg) |

|

[그림] Advanced IC Substrate 시장 성장율 (출처: Yole Intelligence 2023) |

산업통상자원부의 2022년도 기계장비산업기술개발사업 공고에 따르면 현재 솔더볼 마운터는 ATHLETE, SHIBUYA, HITACHI 등 일본 장비기업이 세계시장의 60% 이상을 점유하며 기술을 선도하고 있고, 국내 시장의 경우 0.7억불 규모로 국내 기업은 범프간 피치가 상대적으로 큰 중급 기종에 대한 기술력을 보유하여 중급기종에 대해 국내업체들이 50% 정도로 국내 시장 일부를 점유하고 있으나, 수요가 증가하는 High-End급은 일본메이커가 주도 하고 있습니다. 당사의 제품은 현재 Reflow 및 Deflux 공정 이후 리페어 장비로서 유일하게 양산 검증을 받아 향후 시장을 선점할 수 있습니다.

sLSMB의 시장은 크게 솔더볼의 관점과 산업적 연관성에 따라 아래와 같이 세분화되며, 세그먼트별 시장 수요의 특징은 아래와 같습니다.

|

Segment |

특징 및 진입 장벽 |

|

Flip Chip Scale (40-80㎛) |

고성능 CPU/GPU, AI, Chat Bot 등 SiP 패키징 고도화 FC-BGA 대면적화가 전체 반도체 기판 시장을 주도 대면적화에 따른 Repair 중요성 부각 (수율 보상) 40-80㎛ 초소형 솔더볼 공정으로 기술 진입 장벽 큼 일본, 대만, 한국, 중국 중심 시장 형성 인라인 Full Automation Repair Line 선호 |

|

BGA Scale (150-760㎛) |

1. OSAT 업체가 주요 고객처 형성 2. 소량 다품종 기판 생산 시장 또는 리페어 시장 3. Tact Time과 같은 생산성이 중요한 구매 결정 요소 4. WLP, PLP, HBM 등 신규 시장 확대 속도 빠름 5. Ball Size 소형화로 Repair 수요 증가 |

|

Smart Phone Components (300~700㎛) |

1. Camera Module, VCM, 3D ToF Sensor가 주 시장 2. Semi-Auto Type의 장비 선호 3. 범용성에 대한 요구 높음 4. CIS 외 대부분 소량 다품종 시장 |

[표] sLSMB 세그먼트별 시장 특징

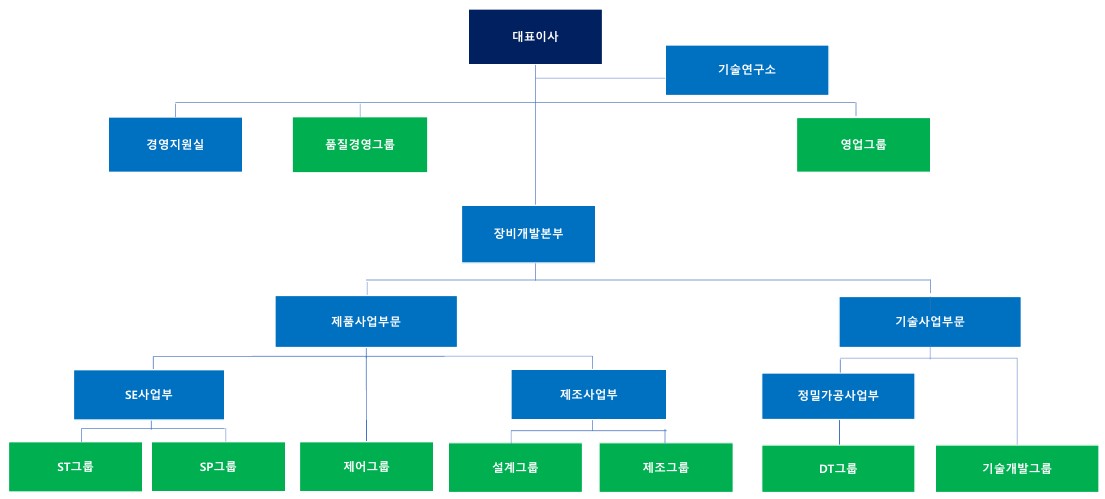

(다) 조직도

|

|

다원넥스뷰 조직도 |

2. 주주총회 목적사항별 기재사항

□ 재무제표의 승인

제1호 의안 : 제16기(2024.1.1-2024.12.31) 재무제표 승인의 건

가. 해당 사업연도의 영업상황의 개요

Ⅲ.경영참고사항의 1. 사업의 개요를 참조하시기 바랍니다.

나. 해당 사업연도의 대차대조표(재무상태표)ㆍ손익계산서(포괄손익계산서)ㆍ자본변동표ㆍ현금흐름표ㆍ이익잉여금처분계산서(안) 또는 결손금처리계산서(안)

※ 아래의 재무제표는 주주총회 승인과정에서 변경될 수 있으며,

외부감사인의 감사의견을 포함한 최종 재무제표는 2025년 3월 19일

전자공시시스템 (http://dart.fss.or.kr)에 공시예정인 당사의

감사보고서를 참조하시기 바랍니다.

1) 연결 재무제표

- 해당사항 없음

2) 별도 재무제표

당사는 한국채택국제회계기준(K-IFRS)준용하여 재무제표를 작성하였습니다.

- 재무상태표

재 무 상 태 표

| 제 16 기 2024년 12월 31일 현재 | |

| 제 15 기 2023년 12월 31일 현재 | |

| 회사명 : 주식회사 다원넥스뷰 | (단위 : 원) |

| 과목 | 제16기말 | 제15기말 | ||

|---|---|---|---|---|

| 자산 | ||||

| 유동자산 | 21,721,642,531 | 11,866,187,185 | ||

| 현금및현금성자산 | 15,987,149,567 | 3,710,236,089 | ||

| 매출채권 | 1,499,374,172 | 573,695,162 | ||

| 재고자산 | 3,985,664,950 | 6,574,876,417 | ||

| 당기법인세자산 | 770,896 | 2,930,720 | ||

| 기타금융자산(유동) | 61,845,192 | 33,423,561 | ||

| 기타자산 | 186,837,754 | 971,025,236 | ||

| 비유동자산 | 6,297,777,495 | 5,023,755,821 | ||

| 유형자산 | 4,839,427,180 | 3,884,429,267 | ||

| 무형자산 | 430,562,875 | 118,731,475 | ||

| 기타금융자산(비유동) | 155,000 | 54,131,692 | ||

| 이연법인세자산 | 1,027,632,440 | 966,463,387 | ||

| 자산총계 | 28,019,420,026 | 16,889,943,006 | ||

| 부채 | ||||

| 유동부채 | 11,727,846,455 | 12,218,964,412 | ||

| 매입채무 | 842,511,428 | 4,189,332,277 | ||

| 차입부채(유동) | 4,000,000,000 | 2,350,000,000 | ||

| 기타금융부채(유동) | 562,851,063 | 805,082,716 | ||

| 리스부채(유동) | 124,148,413 | 107,941,699 | ||

| 판매보증충당부채 | 316,097,166 | 51,767,450 | ||

| 기타유동부채 | 5,882,238,385 | 4,714,840,270 | ||

| 비유동부채 | 975,206,213 | 887,502,819 | ||

| 기타금융부채(비유동) | 61,794,930 | 61,794,930 | ||

| 순확정급여부채 | 820,918,623 | 732,434,529 | ||

| 리스부채(비유동) | 92,492,660 | 93,273,360 | ||

| 부채총계 | 12,703,052,668 | 13,106,467,231 | ||

| 자본 | ||||

| 자본금 | 801,077,200 | 631,250,000 | ||

| 기타불입자본 | 37,753,648,347 | 22,155,835,636 | ||

| 결손금 | (23,238,358,189) | -19,003,609,861 | ||

| 자본총계 | 15,316,367,358 | 3,783,475,775 | ||

| 부채와자본총계 | 28,019,420,026 | 16,889,943,006 | ||

- 포괄손익계산서

포 괄 손 익 계 산 서

| 제16(당)기 2024년 01월 01일부터 2024년 12월 31일까지 | |

| 제15(전)기 2023년 01월 01일부터 2023년 12월 31일까지 | |

| 회사명 : 주식회사 다원넥스뷰 | (단위 : 원) |

| 과목 | 제 16 기 당기 | 제 15 기 전기 | ||

|---|---|---|---|---|

| 매출액 | 18,702,143,953 | 10,653,525,632 | ||

| 매출원가 | 13,891,203,510 | 8,657,830,441 | ||

| 매출총이익 | 4,810,940,443 | 1,995,695,191 | ||

| 판매비와관리비 | 3,531,795,518 | 2,636,658,601 | ||

| 영업이익 | 1,279,144,925 | (640,963,410) | ||

| 기타수익 | 200,509,785 | 505,074,321 | ||

| 기타비용 | 5,607,453,232 | 44,376,398 | ||

| 금융수익 | 202,322,017 | 704,588,442 | ||

| 금융원가 | 238,953,248 | 378,838,468 | ||

| 법인세비용차감전순이익 | (4,164,429,753) | 145,484,487 | ||

| 법인세비용 | (22,036,000) | 56,837,649 | ||

| 당기순이익 | (4,142,393,753) | 88,646,838 | ||

| 기타포괄손익 | (92,354,575) | 25,562,151 | ||

| 후속적으로 당기손익으로 재분류되지 않는 포괄손익: | ||||

| 확정급여제도의 재측정요소 | (92,354,575) | 25,562,151 | ||

| 총포괄손익 | (4,234,748,328) | 114,208,989 | ||

| 주당손익 | ||||

| 기본주당순손익 | (581) | 18 | ||

| 희석주당순손익 | (581) | (54) | ||

- 자본변동표

자 본 변 동 표

| 제16(당)기 2024년 01월 01일부터 2024년 12월 31일까지 | |

| 제15(전)기 2023년 01월 01일부터 2023년 12월 31일까지 | |

| 회사명 : 주식회사 다원넥스뷰 | (단위 : 원) |

| 구분 | 자본금 | 기타불입자본 | 결손금 | 총계 | ||

|---|---|---|---|---|---|---|

| 자본잉여금 | 자본조정 | 계 | ||||

| 2023.01.01(전기초) | 458,750,000 | 4,145,426,475 | - | 4,145,426,475 | (19,117,818,850) | (14,513,642,375) |

| 총포괄손익: | ||||||

| 당기순이익 | - | - | - | - | 88,646,838 | 88,646,838 |

| 상환전환우선주의 전환 | 172,500,000 | 18,010,409,161 | - | 18,010,409,161 | - | 18,182,909,161 |

| 확정급여채무재측정요소 | - | - | - | - | 25,562,151 | 25,562,151 |

| 2023.12.31(전기말) | 631,250,000 | 22,155,835,636 | - | 22,155,835,636 | (19,003,609,861) | 3,783,475,775 |

| 2024.01.01(당기초) | 631,250,000 | 22,155,835,636 | - | 22,155,835,636 | (19,003,609,861) | 3,783,475,775 |

| 총포괄손익: | ||||||

| 당기순이익 | - | - | - | - | (4,142,393,753) | (4,142,393,753) |

| 주식매입선택권 | - | 892,350,000 | - | 892,350,000 | - | 892,350,000 |

| 자기주식의 취득 | - | - | (49,865,190) | (49,865,190) | - | (49,865,190) |

| 합병으로인한 자본변동 | 128,361,100 | 8,941,634,226 | 4,576,164,720 | 13,517,798,946 | - | 13,646,160,046 |

| 전환사채의 전환 | 41,466,100 | 5,813,693,675 | (4,576,164,720) | 1,237,528,955 | - | 1,278,995,055 |

| 확정급여채무재측정요소 | - | - | - | - | (92,354,575) | (92,354,575) |

| 2024.12.31(당기말) | 801,077,200 | 37,803,513,537 | (49,865,190) | 37,753,648,347 | (23,238,358,189) | 15,316,367,358 |

- 현금흐름표

현 금 흐 름 표

| 제16(당)기 2024년 01월 01일부터 2024년 12월 31일까지 | |

| 제15(전)기 2023년 01월 01일부터 2023년 12월 31일까지 | |

| 회사명 :주식회사 다원넥스뷰 | (단위 : 원) |

| 구분 | 제 16 기 당기 | 제 15 기 전기 | ||

|---|---|---|---|---|

| 영업활동으로 인한 현금흐름 | 1,248,454,220 | 3,058,011,548 | ||

| 당기순손익 | (4,142,393,753) | 88,646,838 | ||

| 조정 | 8,052,784,422 | 428,309,802 | ||

| 감가상각비 | 617,222,048 | 550,313,985 | ||

| 무형자산상각비 | 91,233,100 | 194,666,403 | ||

| 유형자산처분이익 | (4,052) | - | ||

| 주식기준보상 | 892,350,000 | - | ||

| 퇴직급여 | 340,613,615 | 318,857,633 | ||

| 대손상각비 | 23,509,719 | 835,039 | ||

| 재고자산평가손실(환입) | 652,663,827 | (371,238,683) | ||

| 이자비용 | 238,953,248 | 378,838,468 | ||

| 판매보증비(환입) | 671,286,583 | (1,630,080) | ||

| 외화환산손실 | 1,638,137 | 13,999,293 | ||

| 법인세비용(수익) | (22,036,000) | 56,837,649 | ||

| 이자수익 | (202,322,017) | (23,224,602) | ||

| 잡이익 | - | (7,425,677) | ||

| 외화환산이익 | (48,452,792) | (1,155,786) | ||

| 파생상품평가이익 | - | (681,363,840) | ||

| 합병비용 | 4,796,129,006 | - | ||

| 영업활동으로 인한 자산부채의 변동 | (2,890,251,926) | 2,638,253,216 | ||

| 매출채권의 증감 | (936,233,625) | (83,639,613) | ||

| 재고자산의 증감 |

11,177,196 | (3,064,798,989) | ||

| 기타금융자산의 증감 |

44,585,966 | 160,392,002 | ||

| 기타자산의 증감 |

784,187,482 | (703,949,675) | ||

| 매입채무의 증감 |

(3,346,820,849) | 3,568,974,487 | ||

| 기타금융부채의 증감 |

(245,587,698) | 439,949,985 | ||

| 기타부채의 증감 |

1,167,325,855 | 2,580,071,916 | ||

| 판매보증충당부채의 증감 |

- | (103,937,518) | ||

| 퇴직금의 지급 | (68,886,253) | (154,809,379) | ||

| 사외적립자산의 증감 |

(300,000,000) | - | ||

| 이자의 수취 | 476,105,923 | 20,143,916 | ||

| 이자의 지급 | (177,147,266) | (114,701,084) | ||

| 법인세의 납부 | (70,643,180) | (2,641,140) | ||

| 투자활동으로 인한 현금흐름 | 9,521,749,187 | (1,013,563,975) | ||

| 유형자산의 취득 | (304,469,236) | (955,196,575) | ||

| 무형자산의 취득 | (18,064,500) | (20,867,400) | ||

| 보증금의 증가 | (4,000,000) | (39,991,860) | ||

| 보증금의 감소 | - | 2,491,860 | ||

| 합병으로 인한 증가 | 1,708,460,793 | - | ||

| 장기금융상품의 처분 | 8,139,822,130 | - | ||

| 재무활동으로 인한 현금흐름 | 1,471,246,970 | (160,560,000) | ||

| 단기차입금의 차입 | 6,000,000,000 | - | ||

| 단기차입금의 상환 | (4,350,000,000) | (50,000,000) | ||

| 리스부채의 지급 | (132,619,030) | (110,560,000) | ||

| 자기주식의 취득 | (46,134,000) | - | ||

| 현금및현금성자산의 증감 | 12,241,450,377 | 1,883,887,573 | ||

| 기초 현금및현금성자산 | 3,710,236,089 | 1,839,917,200 | ||

| 외화표시 현금및현금성자산의 환율변동 효과 | 35,463,101 | (13,568,684) | ||

| 기말 현금및현금성자산 | 15,987,149,567 | 3,710,236,089 | ||

- 이익잉여금처분계산서(결손금처리계산서)(안)

이익잉여금처분계산서 (결손금처리계산서)(안)

| 제16(당)기 2024년 01월 01일부터 2024년 12월 31일까지 | |

| 제15(전)기 2023년 01월 01일부터 2023년 12월 31일까지 | |

| 처리예정일 2025년 03월 27일 | 처리확정일 2024년 03월 26일 |

| 회사명 : 주식회사 다원넥스뷰 | (단위 : 원) |

| 구분 | 제 16 기 당기 | 제 15 기 전기 | ||

|---|---|---|---|---|

| 처리예정일: 2025년 3월 27일 | 처리확정일: 2024년 3월 26일 | |||

| 미처리결손금 | (23,238,358,189) | (19,003,609,861) | ||

| 전기이월미처리결손금 | (19,003,609,861) | (19,117,818,850) | ||

| 당기순이익 | (4,142,393,753) | 88,646,838 | ||

| 확정급여제도의 재측정요소 | (92,354,575) | 25,562,151 | ||

| 결손금처리액 | - | - | ||

| 차기이월미처리결손금 | (23,238,358,189) | (19,003,609,861) | ||

※ 상세한 주석사항은 2025년 3월 19일 전자공시시스템(http://dart.fss.or.kr)과 당사 홈페이지(http://www.nexview.co.kr/, 고객지원→게시판→감사/검토보고서)에 공시예정인 당사의 감사보고서를 참조하시기 바랍니다.

- 최근 2사업연도의 배당에 관한 사항

해당사항 없습니다.

□ 정관의 변경

가. 집중투표 배제를 위한 정관의 변경 또는 그 배제된 정관의 변경

| 변경전 내용 | 변경후 내용 | 변경의 목적 |

|---|---|---|

| 해당사항 없음 | 해당사항 없음 | 해당사항 없음 |

나. 그 외의 정관변경에 관한 건

| 변경전 내용 | 변경후 내용 | 변경의 목적 |

|---|---|---|

| 제2조(목적) 당 회사는 다음 사업을 경영함을 목적으로 한다. 1. 바이오, 의료장비 제조, 판매업 2. 보안장비 제조, 판매업 3. 검사장비 제조, 판매업 4. 위 각호와 관련된 장비 수출입업 5. Know-How, 기술의 판매, 임대업 6. 기타 부대사업 일체 |

제2조(목적) 당 회사는 다음 사업을 경영함을 목적으로 한다. 1. 반도체 장비 제조 및 판매업 2. 레이저 응용장비 제조 및 판매업 3. 바이오, 의료장비 제조, 판매업 4. 보안장비 제조, 판매업 5. 검사장비 제조, 판매업 6. 위 각호와 관련된 장비 수출입업 7. Know-How, 기술의 판매, 임대업 8. 기타 부대사업 일체 |

관련 사업 명문화 |

| 부칙 이 정관은 2023년 06월 29일 시행한다. |

부칙 이 정관은 2025년 03월 27일 시행한다. |

※ 기타 참고사항

- 해당사항 없음

□ 이사의 선임

제3-1호 의안 : 비상무이사 박병철 신규 선임의 건

가. 후보자의 성명ㆍ생년월일ㆍ추천인ㆍ최대주주와의 관계ㆍ사외이사후보자 등 여부

| 후보자성명 | 생년월일 | 사외이사 후보자여부 |

감사위원회 위원인 이사 분리선출 여부 |

최대주주와의 관계 | 추천인 |

|---|---|---|---|---|---|

| 박병철 | 900218 | 기타비상무이사 | 해당사항 없음 | 특수관계자 | 이사회 |

| 총 ( 1 ) 명 | |||||

나. 후보자의 주된직업ㆍ세부경력ㆍ해당법인과의 최근3년간 거래내역

| 후보자성명 | 주된직업 | 세부경력 | 해당법인과의 최근3년간 거래내역 |

|

|---|---|---|---|---|

| 기간 | 내용 | |||

| 박병철 | 경영컨설턴트 | 2017.11~2020.08 2020.12~2022.02 2022.03~2023.06 |

IBM Global Business Services 경영컨설턴트 EY-Parthenon 경영컨설턴트 삼성글로벌리서치 수석연구원 |

- |

다. 후보자의 체납사실 여부ㆍ부실기업 경영진 여부ㆍ법령상 결격 사유 유무

| 후보자성명 | 체납사실 여부 | 부실기업 경영진 여부 | 법령상 결격 사유 유무 |

|---|---|---|---|

| 박병철 | 해당사항 없음 | 해당사항 없음 | 해당사항 없음 |

라. 후보자의 직무수행계획(사외이사 선임의 경우에 한함)

| 해당사항 없음 |

마. 후보자에 대한 이사회의 추천 사유

| □박병철 사내이사 후보자 본 후보자는 KAIST 경영대학 기술경영학 석사과정을 마치고 경영컨설턴트로서 IBM Global Business Services와 EY-Parthenon에서 재임하였으며 삼성글로벌리서치 수석연구원으로 일하며 경영전반에 관한 전문성과 통찰력을 갖추고 있습니다. 이에 당사의 기업가치를 높일 수 있는 적임자로 판단되어 박병철 후보자를 기타비상무이사로 추천합니다. |

확인서

|

|

사내이사 박병철 확인서 |

※ 기타 참고사항

- 해당사항 없음

□ 감사의 선임

제4-1호 의안 : 감사 한일영 신규 선임의 건

<감사후보자가 예정되어 있는 경우>

가. 후보자의 성명ㆍ생년월일ㆍ추천인ㆍ최대주주와의 관계

| 후보자성명 | 생년월일 | 최대주주와의 관계 | 추천인 |

|---|---|---|---|

| 한일영 | 720111 | 해당사항 없음 | 이사회 |

| 총 ( 1 ) 명 | |||

나. 후보자의 주된직업ㆍ세부경력ㆍ해당법인과의 최근3년간 거래내역

| 후보자성명 | 주된직업 | 세부경력 | 해당법인과의 최근3년간 거래내역 |

|

|---|---|---|---|---|

| 기간 | 내용 | |||

| 한일영 | 슈어소프트테크 CSO | 2001.01~2003.04 2003.04~2005.12 2006.01~2011.10 2011.10~현재 |

Lawrence Livermore National Laboratory Post Doc ㈜LG CNS 선임컨설턴트 삼성경제연구소 수석연구원 슈어소프트테크 전략담당 (Chief Strategy Officer, CSO) |

- |

다. 후보자의 체납사실 여부ㆍ부실기업 경영진 여부ㆍ법령상 결격 사유 유무

| 후보자성명 | 체납사실 여부 | 부실기업 경영진 여부 | 법령상 결격 사유 유무 |

|---|---|---|---|

| 한일영 | 해당사항 없음 | 해당사항 없음 | 해당사항 없음 |

라. 후보자에 대한 이사회의 추천 사유

| □한일영 감사 후보자 본 후보자는 결격사유가 존재하지 아니하며, 슈어소프트테크에서 전략담당 최고책임자 (CSO)로서의 경험을 바탕으로 기업 전략 및 경영에 대한 깊은 이해를 가지고 있습니다. 또한 삼성경제연구소와 LG CNS에서의 경력을 통해 다각적인 산업 및 시장 분석 능력을 보유하고 있어 기업가치 증진과 지속적 성장에 기여할 적임자로 판단됩니다. |

확인서

|

|

감사 한일영 확인서 |

※ 기타 참고사항

- 해당사항 없음

□ 이사의 보수한도 승인

가. 이사의 수ㆍ보수총액 내지 최고 한도액

(당 기)

| 이사의 수 (사외이사수) | 6 (3) |

| 보수총액 또는 최고한도액 | 1,500백만원 |

(전 기)

| 이사의 수 (사외이사수) | 5 (3) |

| 실제 지급된 보수총액 | 544백만원 |

| 최고한도액 | 1,000백만원 |

※ 기타 참고사항

- 해당사항 없음

□ 감사의 보수한도 승인

가. 감사의 수ㆍ보수총액 내지 최고 한도액

(당 기)

| 감사의 수 | 1 |

| 보수총액 또는 최고한도액 | 60백만원 |

(전 기)

| 감사의 수 | 1 |

| 실제 지급된 보수총액 | 12백만원 |

| 최고한도액 | 60백만원 |

※ 기타 참고사항

- 해당사항 없음

IV. 사업보고서 및 감사보고서 첨부

가. 제출 개요

| 제출(예정)일 | 사업보고서 등 통지 등 방식 |

|---|---|

| 2025년 03월 19일 | 1주전 회사 홈페이지 게재 |

나. 사업보고서 및 감사보고서 첨부

당사는 2025년 3월 19일 사업보고서 및 감사보고서를 전자공시시스템(http://dart.fss.or.kr)에 공시하고 당사 홈페이지(http://www.nexview.co.kr/, 고객지원→게시판→감사/검토보고서)에 게재할 예정입니다.

향후 이 사업보고서는 주주총회 이후 변경되거나 오기 등이 있는 경우 수정될 수 있으며, 이 경우 전자공시시스템(http://dart.fss.or.kr)에 정정보고서를 공시할 예정이므로 이를 참조하시기 바랍니다.

※ 참고사항

| □ 주총 집중일 주총 개최 사유 - 당사는 제16기 정기주주총회와 관련하여 주주총회 집중일을 피하여 개최하고자 하였으나, 외부감사인의 감사일정, 감사보고서 제출일정, 주요 경영일정 및 주주총회 운영일정 등을 고려하여 불가피하게 집중일인 2025년 03월 27일(목)에 주주총회를 개최하게 되었습니다. - 코스닥협회가 발표한 당해년도 주주총회 집중(예상)일 : 3월 21일(금), 3월 27일(목), 3월 28일(금) |